# Article Approaches to Extend FPGA Reverse-Engineering Technology from ISE to Vivado

Soyeon Choi and Hoyoung Yoo \*

Department of Electronics Engineering, Chungnam National University, Daejeon 34134, Republic of Korea; soyeonchoi@cnu.ac.kr

\* Correspondence: hyyoo@cnu.ac.kr

Abstract: SRAM-based FPGA(Field Programmable Logic Arrays) requires external memory since its internal memory gets erased when power is cut off. The process of transmitting the circuit netlist in bitstream from external memory during power-up in FPGA is vulnerable to malicious attacks such as bitstream theft and tampering. Previous FPGA reverse-engineering methods focus on FPGAs, supported by ISE (ISE Design Suite). This is because ISE provides XDLRC (Xilinx Design Language Routing Configurable logic) and XDL (Xilinx Design language) files, which are essential for reverse engineering. However, Vivado Design Suite (Vivado) does not offer those files, making it impossible to extend the coverage of reverse engineering to the FPGAs supported by Vivado. In this paper, we propose a method to generate XDLRC and XDL through Vivado. According to experimental results, the XDLRC and XDL generated through Vivado, respectively, match 99% and 75% with those generated in ISE for Artix-7 100T. As a result, this paper has expanded the scope of reverse engineering from being mainly focused on ISE to now also include Vivado. It is important to note that this paper does not encourage bitstream attacks through reverse engineering but rather highlights the risk associated with malicious attacks and emphasizes the importance of security.

Keywords: reverse engineering; Xilinx; Vivado design suite; ISE design suite; Xilinx design language file

Citation: Choi, S.; Yoo, H. Approaches to Extend FPGA Reverse-Engineering Technology from ISE to Vivado. Electronics 2024, 13, 1100. https:// doi.org/10.3390/electronics13061100

Academic Editors: Raffaele Giordano and Alexander Barkalov

Received: 6 February 2024 Revised: 4 March 2024 Accepted: 14 March 2024 Published: 16 March 2024

Copyright: © 2024 by the authors. Licensee MDPI, Basel, Switzerland, This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

## 1. Introduction

SRAM-based FPGAs, along with the Flash-based FPGA (Field Programmable Logic Array) and the Antifuse-based FPGA, play a significant role in various applications, such as signal processing, communication systems, image processing, control systems, encryption, and security [1]. Notably, AMD Xilinx and Intel Altera FPGAs demonstrate the highest market share in the SRAM-based FPGA industry [2]. FPGA chip manufacturers typically provide EDA tools to support circuit synthesis and implementation on FPGA chips, with Xilinx offering two such tools: ISE (ISE Design Suite) for low-power, low-end FPGAs [3], and Vivado (Vivado Design Suite) for the latest high-end FPGAs [4]. Specifically, ISE supports older FPGA series up to 7-series and some low-end 7-series FPGAs [3], while Vivado supports all 7-series and subsequent state-of-the-art FPGAs [4]. Table 1 summarizes the FPGA-specific support Design Suite for each Xilinx FPGA, where Virtex and Kintex series FPGAs generally have larger chip sizes and are fabricated using more advanced processes compared to Spartan and Artix series FPGAs [5].

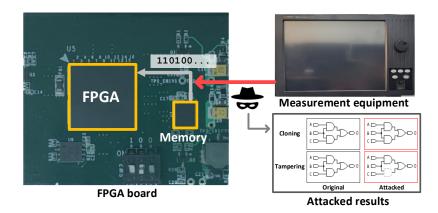

Through the diverse FPGA chip portfolio provided by FPGA manufacturers and the stability of EDA tools, FPGA applications have expanded significantly. However, SRAMbased FPGAs have a critical drawback, which is that they require external memory since their internal memory gets erased when power is cut off [6]. The process of transmitting the netlist in bitstream format from external memory during power-up in FPGA systems makes it vulnerable to malicious attacks like bitstream theft and tampering, as shown in Figure 1 [7–9]. The complete extraction of the bitstream enables the potential for a cloning

attack, and tampering with the hardware results in malfunctions, leading to potential damage. Additionally, intelligent reverse engineering [10–21] can be utilized to analyze the design of the netlist. When a circuit is attacked, the circuit does not behave as intended, causing serious problems. In the case of reverse engineering, all circuit information is exposed to the attacker, causing serious problems with circuit security.

| Family  | Series      | ISE | Vivado |

|---------|-------------|-----|--------|

|         | 3           | 0   | Х      |

| Spartan | 6           | О   | Х      |

| -       | 7           | Х   | О      |

|         | 5           | О   | Х      |

|         | 6           | О   | Х      |

| Virtex  | 7           | Δ   | О      |

|         | UltraScale  | Х   | О      |

|         | UltraScale+ | Х   | О      |

| A       | 7           | О   | О      |

| Artix   | UltraScale+ | Х   | О      |

|         | 7           | 0   | О      |

| Kintex  | UltraScale  | Х   | О      |

|         | UltraScale+ | Х   | О      |

Table 1. Design Suites available for each FPGA series.

Figure 1. How to attack the FPGA system.

The previous FPGA reverse-engineering tools primarily focus on FPGAs supported by ISE, as shown in Table 1. The FPGAs that have been targeted by reverse engineering are mostly devices in the Spartan-3 series and Virtex-5 series in previous research [10–14]. This is because ISE provides of readable XDLRC (Xilinx Design Language Routing Configurable logic) and XDL (Xilinx Design language) files [22]. Note that the XDLRC file is a hardware structure file, and the XDL file is the netlist file provided by ISE. Based on XDLRC, the previous FPGA reverse-engineering techniques [10–14] identify the association between XDL and bitstream. The association is converted into a database that is used for reverse engineering. All hardware elements in the FPGA described in XDLRC appear in the bitstream, and the value is 1 in the bitstream only for the hardware elements used in XDL. The database is generated by modifying the XDL files that applying information on XDLRC and comparing bitstreams. Therefore, XDL and XDLRC files are essential for securing a database for reverse engineering. Although some reverse-engineering techniques using Vivado have been announced [15-21], the techniques are very limited and still at a rudimentary level. The reason the latest FPGA reverse-engineering techniques in Vivado are restricted and disturbed is the absence of textual netlist files such as XDLRC and XDL. Consequently, this paper proposes a method to generate XDLRC and XDL files in Vivado, similar to those in ISE, to extend the coverage of the previous reverse-engineering techniques. It is important to note that this paper does not encourage bitstream attacks through reverse engineering but rather highlights the risk associated with malicious attacks and emphasizes the importance of security. The remaining sections of this paper are organized as follows: Section 2 explains the structure of Xilinx FPGAs and the design flow of ISE and Vivado. In Section 3, we verify XDL and XDLRC files generated using ISE and propose a method to generate them using Vivado. Section 4 analyzes the differences between the files generated by the two EDA tools. Finally, Section 5 presents the conclusions of this paper.

## 2. Background

In Xilinx FPGA devices, the XDLRC file represents a textual description of all available hardware resources within the FPGA device, while the XDL file specifically details the activated resources among the entire hardware [22]. To properly comprehend XDLRC and XDL files, it is fundamental to grasp the fundamental structure of Xilinx FPGA devices. In this chapter, we provide a comprehensive overview of the inherent hierarchical structure of Xilinx FPGA architectures. Following that, we outline the sequential procedures for circuit synthesis, implementation, and bitstream generation using both the ISE and Vivado.

## 2.1. Structure of Xilinx FPGA

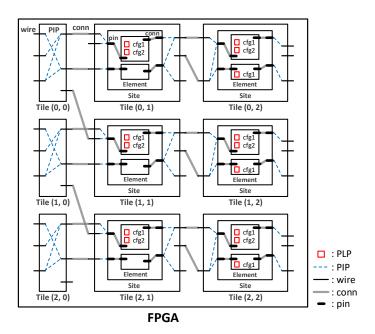

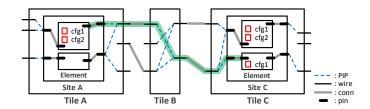

Xilinx FPGAs feature a hierarchical structure for their hardware resources, which can be simplified as depicted in Figure 2 [23–30]. The interior of the FPGA is composed of tiles. The positions of these tiles are defined using Cartesian coordinates (X, Y). The interconnections between tiles are fixed, and these static connections within the FPGA are referred to as conn. The input and output ports of the tiles are defined as wires, and the internal connections between wires are denoted as PIPs (Programmable Interconnect Points). Each wire can be connected to one or more PIPs, with the appropriate PIPs selected depending on the circuit implementation.

Figure 2. Hierarchical structure of FPGA.

Within each tile, there is a sub-level block known as a *site*. The input and output ports of the site are defined as *pin*, and the connections between pins are also represented as *conn*. Inside the site, there is another sub-level block called an *element*. Like the site, the input and output ports of the element are composed of *pins*. Elements can either include or exclude a configurable logical option referred to as *cfg*. Among elements that include *cfg*, those responsible for constructing logic elements such as MUXs (Multiplexers) are called PLPs

(Programmable Logic Points), while those supporting data storage functions like LUTs (Look-Up Tables) are termed PDPs (Programmable Data Points).

## 2.2. ISE Design Flow

The design flow in ISE, from circuit synthesis to implementation, is depicted in Figure 3. As shown in Figure 3, the ISE design flow comprises a total of five stages, each executed using Tcl commands. The process begins with synthesis, which requires HDL source files, including the design, and a UCF (User Constraint File) file specifying constraints. Once these two files are prepared, synthesis is initiated using the '*xst*' command. After synthesis, an NGC (Native Generic Constraint) file is generated, combining the design and constraints.

Figure 3. ISE design flow.

Following that, the '*ngdbuild*' stage is executed, which assigns the information described in the NGC file to the physical resources of the FPGA, generating the NGD (Native Generic Database) file, which includes routing and timing details in the form of a netlist. After this, during the '*map*' stage, the physical resources outlined in the NGD file are mapped to real hardware components such as LUTs, MUXs, and BRAMs (Block RAMs). Finally, when the '*par*' stage, responsible for P&R (Placement and Routing), is executed, it results in the generation of the netlist files, the NCD (Native Circuit Description) file, and the XDL file. While netlist files such as NGC and NGD, including the NCD file, are all in a binary format, the XDL file is in textual format, making it user-readable. Once the P&R process is completed, the netlist files can be transformed into a BIT file, which can be programmed onto the FPGA, via the '*bitgen*' stage. It is noteworthy that, within the ISE, the XDLRC file, describing all available hardware resources within the FPGA, can be generated at any stage of the design flow after project creation.

## 2.3. Vivado Design Flow

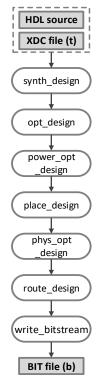

Vivado, on the other hand, follows a design flow consisting of a total of seven stages, as depicted in Figure 4. In the Vivado design flow, it is essential to have both the HDL source, comprising the design, and the XDC file, detailing the constraints. Once these two files are prepared, circuit synthesis is performed using the 'synth\_design' command.

After synthesis, the implementation proceeds through five stages. As the initial step of implementation, *'opt\_design'* is performed to optimize the synthesis results, followed by *'power\_opt\_design'* to further optimize from a power perspective.

Figure 4. Vivado design flow.

Following that, 'place\_design' is responsible for positioning the optimized design onto the FPGA hardware resources, while 'phys\_opt\_design' focuses on optimization with regard to physical placement. Afterward, 'route\_design' manages routing, and the 'write\_bitstream' stage generates the BIT file that can be programmed onto the FPGA. It is important to note that no netlist files, including XDL files, are generated during the synthesis and implementation stages in Vivado design flow, and XDLRC files are also not provided.

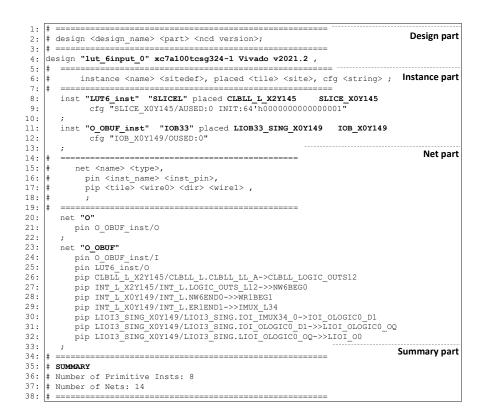

#### 3. Netlist File Generation

The XDLRC is essential for understanding the hardware structure, and the XDL shows that the hardware elements appear in the bitstream as a readable netlist. These two files are extracted from ISE with a single Tcl command in ISE, but in Vivado, they are extracted with multiple Vivado Tcl commands. This section describes how to extract XDLRC and XDL files from ISE and Vivado.

#### 3.1. XDLRC File Generated by ISE

An XDLRC file can be generated using a Tcl command in ISE, and the Tcl command to create an XDLRC file is as follows:

## *xdl* -report [-pips] [-all\_conns] <part> [<outfile name>]

The options [*-pips*] and [*-all\_conns*] are used with the '*xdl -report*' command. [*-pips*] generates a report containing pip routing information, while [*-all\_conns*] displays all connections to a tile wire, regardless of the containing adjacent tile. The <part> parameter represents the FPGA device, and it should include the speed grade and package details. [*<outfile name>*] is an optional parameter; if not specified, the XDLRC file will be created with a default name following the pattern '*<part>.xdlrc*'.

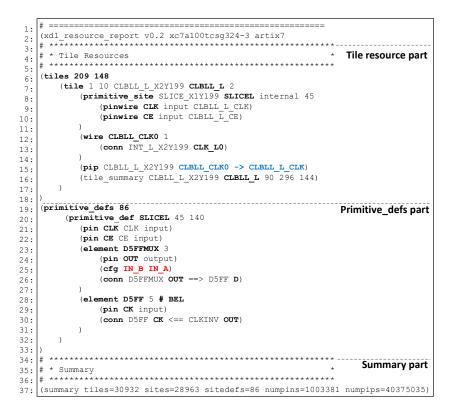

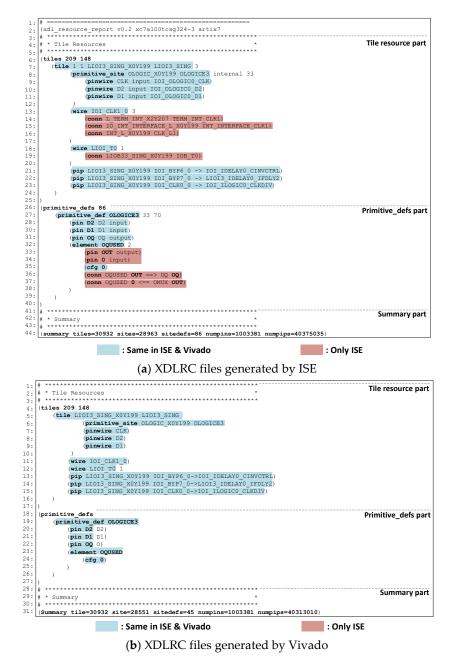

As an example in this paper, the Artix-7 100t device, with a speed grade of -1 and 324 external I/O pads in the csg324 package, is used. If you want to generate an XDLRC file to list the tiles and sites included for this device, '*xdl*-*report xc7a100t*-1*csg324*' should be executed to generate the XDLRC file. However, if you wish to obtain comprehensive information, including all pips, wires, and conns for the same device, '*xdl*-*report -pips -all\_conns xc7a100t*-1*csg324*' should be executed to generate the XDLRC file generated using the options [-pips] and [-all\_conns]. The XDLRC file, as seen in Figure 5, consists of three parts: the tile resource part, the primitive\_defs part, and the summary part.

Figure 5. XDLRC generated by ISE.

The Tile resource part represents all of the FPGA hardware resources at the tile level, starting from the tile at position (0, 0) and describing each tile position, tile name, and tile type. In Figure 5, line 7 begins to depict the internal structure of the tile located at (1, 10). The numbers 1 and 10 represent the X and Y coordinates of the tile, respectively. The subsequent CLBLL\_L\_X2Y199 indicates the tile name, with CLBLL\_L denoting the tile type. The number, 2, signifies the number of sites contained within this tile. Line 8 provides information about the sites configured within the tile. The sites are declared as primitive\_site. The SLICE\_X1Y199 indicates the site name, SLICEL represents the site type, and *internal* 45 specifies that the site contains 45 pins. Lines 9 and 10 detail the site pins and wires. In the tile resource part, the internal structure of the tile is described by only the site pins. Following primitive\_site, the wires associated with the tile are listed. At a lower level of wire, the conn describes how each wire is linked, specifying which tile wire it connects to. Therefore, through lines 12 and 13, we can discern that the CLBLL\_CLK0 wire is connected to the CLK\_L0 wire of INT\_L\_X2Y199 via the conn. The last line representing the tile includes the tile name, type, the number of pinwires, wires, and pips present in the tile.

In the primitive\_defs part, the complete internal structures of all sites included in this device are shown. Line 19 marks the beginning of revealing the internal structure of the *SLICEL* site, with the numbers 45 and 140 following *SLICEL* signifying the respective

counts of input/output pins and elements within the site. Each pin in the section describes the pin name, the associated pinwire name from the tile resource part, and whether the pin functions as an input or output represented in line 21 and line 22. The details of the elements appear, as seen in line 23, where the element name and a number denoting the number of pins within the element are provided. If there is a configuration present representing *cfg* in Figure 6, all configurations of the element are listed, like line 25. The *conn* of the elements represent the connections between pins of the elements. For instance, line 26 signifies the connection between the *OUT* pin of the *D5FFMUX* element and the *D* pin of the *D5FF* element. When the line beginning with the element name in the primitive\_defs part is suffixed with # *BEL*, it indicates that this element serves as a basic element as representing *bel* in Figure 6, such as an LUT or an FF(Flip-Flop).

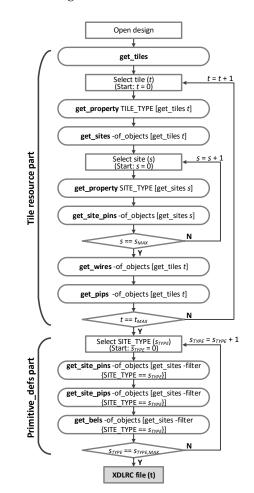

Figure 6. Flow chart for generating XDLRC with Vivado.

In the summary part, details regarding the number of tiles, sites, site types, site input/output pin counts, and the number of PIPs encompassed by this device are presented.

#### 3.2. XDLRC File Generated by Vivado

In Vivado, there is no Tcl command like '*xdl-report*' to generate an XDLRC file. However, through Vivado Tcl commands supported by Vivado, it is possible to obtain information about FPGA hardware resources and create an XDLRC file.

To construct the tile resource part of the XDLRC file, information about tile names, tile types, sites within the tile, wires and conns contained within the tile, and pips are required. To access this information, commands such as 'get\_tiles', 'get\_sites', 'get\_wires', and 'get\_pips' are demanded. These commands alone provide only the names of each component.

Identifying tile types and site types corresponds to particular attributes referred to as TILE\_TYPE and SITE\_TYPE. To access these properties, the 'get\_property' command should be employed. It is important to note that extracting information about fixed connections conn with Tcl commands in Vivado is not feasible.

The primitive\_defs part, which describes the internal structure of each site type, requires information about the pins within the site, the *cfg* of elements, *conn*, and whether an element is a *bel*. Information regarding the pins within a site can be obtained through the use of the '*get\_site\_pins*' command. The configuration of an element, which represents the programmable points within the site, can be obtained using the '*get\_site\_pips*' command. Elements that are *bels* can be distinguished using '*get\_bels*'. However, it is important to note that extracting conn, similar to the tile resource part, is not feasible through available commands.

Figure 6 illustrates the process of generating an XDLRC file in Vivado as a flowchart. To create the tile resource part, the process of extracting the required information for each tile is repeated for all tiles. For the primitive\_defs part, the process of discovering internal site details is repeated for each site type. The summary part determines the count of each component using the Tcl command *'llength'*. Through these steps, the XDLRC file was created in Vivado, as shown in Figure 7.

| 1:         | # *************************************                      | Tile resource part  |

|------------|--------------------------------------------------------------|---------------------|

| 2:         | # * Tile Resources *                                         | The resource part   |

| 3:         | # *************************************                      |                     |

| 4:         | (tiles 209 148                                               |                     |

| 5:         | (tile CLBLL L X2Y199 CLBLL L                                 |                     |

| 6:         | (primitive site SLICE X1Y199 SLICEL                          |                     |

| 7:         |                                                              |                     |

| 8:         |                                                              |                     |

| 9:         | (wire CLBLL CLK0)                                            |                     |

| 10:        | (pip CLBLL L X2Y199 CLBLL CLK0->CLBLL L CLK)                 |                     |

| 11:        |                                                              |                     |

| 12:        |                                                              |                     |

| 13:        | (primitive defs                                              | Primitive defs part |

| 14:        | (primitive def SLICEL                                        | rinneve_dels pare   |

| 15:        | (pin CE)                                                     |                     |

| 16:        | (pin CLK)                                                    |                     |

| 17:        | (cfg DFFMUX:05)                                              |                     |

| 18:<br>19: | (cfg DFFMUX:06)                                              |                     |

|            | (bel DFF)                                                    |                     |

| 20:        | # *************************************                      | Summary part        |

| 21:        | # * Summary *                                                | Summary part        |

| 22:        | # *************************************                      |                     |

| 23:<br>24: | (Summary tile=30932 site=28551 sitedefs=45 numpins=1003381 r | numpips=40313010)   |

Figure 7. XDLRC generated by Vivado.

## 3.3. XDL File Generated by ISE

The TCL command for creating an XDL file using ISE is as follows:

xdl -ncd2xdl [-nopips] <ncdfile name> [<xdlfile name>]

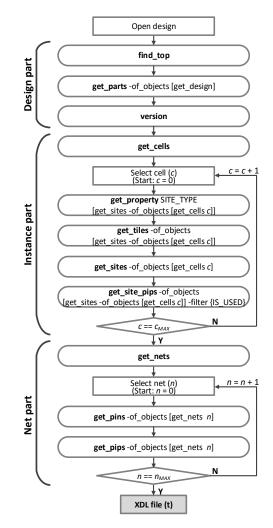

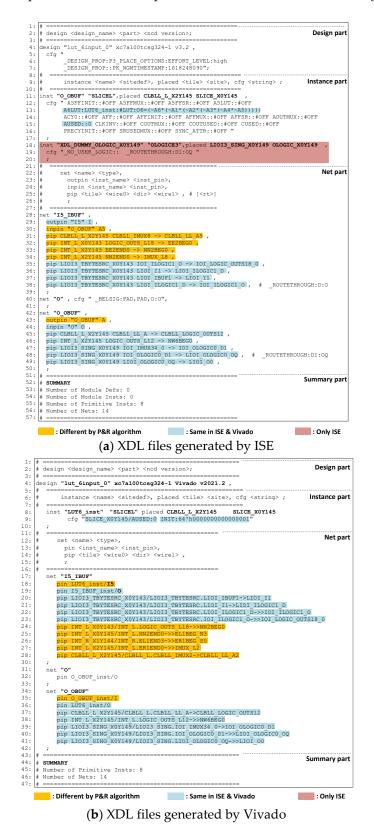

[-*nopips*] is an option for the '*xdl-ncd2xdl*' command that suppresses the reporting of PIPs, and <*ncdfile name>* is the name of the netlist file generated after performing P&R, typically matching the top module name. [<*xdlfile name>*] is an optional parameter to specify the output file name. If the output file name is not specified, an XDL file with the same name as the NCD file is generated. For instance, if the top module name 'TestDesign\_v1.xdl', the Tcl command should be written as follows: '*xdl -ncdtoxdl TestDesign.ncd TestDesign\_v1.xdl'*. An example of an XDL file generated using the '*xdl-ncd2xdl'* command in ISE is illustrated in Figure 8 and is structured in four parts: the design part, the instance part, the net part, and the summary part. In the design part, information such as the design name, device type, and the version of ISE are presented.

The instance part displays hardware resources used in the design implementation at the cell. A cell can be either a primitive or a hierarchical instance within a netlist. Examples of cells include FFs, LUTs, I/O buffers, and hierarchical instances. The first line representing

information about a single cell, as seen in line 11 of Figure 8, and includes the cell name, the site type and site name where the cell is implemented, and the name of the tile where it is located. Following the keyword *cfg* on the next line are all PLPs contained within the site, used for the circuit implementation, listed along with their respective configurations. Unused PLPs are marked with #*OFF* in the configuration string, while PDPs display data stored as Boolean functions.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | sign <design_name> <part> <ncd version="">; Design part</ncd></part></design_name>                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | gn "lut_6input_0" xc7a100tcsg324-1 v3.2 ,                                                                                                                                                                                                                                                                                                                                                                                 |

| : c:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | g "                                                                                                                                                                                                                                                                                                                                                                                                                       |

| :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _DESIGN_PROP:P3_PLACE_OPTIONS:EFFORT_LEVEL:high                                                                                                                                                                                                                                                                                                                                                                           |

| :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _DESIGN_PROP::PK_NGMTIMESTAMP:1618248090";                                                                                                                                                                                                                                                                                                                                                                                |

| : # =<br>: #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | instance <name> <sitedef>, placed <tile> <site>, cfg <string> ; Instance par</string></site></tile></sitedef></name>                                                                                                                                                                                                                                                                                                      |

| : # :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | instance (name) (siteder), praced (tite) (site), cig (string),                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | "O OBUF" "SLICEL", placed CLBLL L X2Y145 SLICE X0Y145 ,                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | a " ASFFINIT::#OFF ASFFMUX::#OFF ASFFSR::#OFF ASLUT::#OFF                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A6LUT:LUT6 inst:#LUT:O6=(~A6*(~A1*(~A2*(~A3*(~A4*~A5))))))                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ACY0::#OFF AFF::#OFF AFFINIT::#OFF AFFMUX::#OFF AFFSR::#OFF AOUTMUX::#OFF                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | AUSED::0 CLKINV::#OFF COUTMUX::#OFF COUTUSED::#OFF CUSED::#OFF                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PRECYINIT::#OFF SRUSEDMUX::#OFF SYNC ATTR::#OFF "                                                                                                                                                                                                                                                                                                                                                                         |

| ; ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Insertation skoolshokgort sine_artkgort                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | "XDL DUMMY OLOGIC X0Y149" "OLOGICE3", placed LIOI3 SING X0Y149 OLOGIC X0Y149                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | g " NO USER LOGIC:: ROUTETHROUGH:D1:00 "                                                                                                                                                                                                                                                                                                                                                                                  |